服务热线

18574304394

2024-03-30 17:47:00

由深圳瑞沃微半导体科技有限公司发布 | 2024-03-30 深圳

半导体封装方案目前各类层出不穷,具体有何差别,芯片封装是提升芯片性能的另一个方向,主要是指采用具有一定强度和导电导热或绝缘特性的材料对芯片进行外层包覆,以实现对芯片的物理保护及电气连接,使芯片电光转换效率等关键性能得以充分释放,同时不受水、电、尘渍、撞击等外界干扰,保持芯片稳定工作能力的一种技术的统称,诸如倒装芯片封装,晶圆级封装等先进封装技术将带来新一轮的芯片性能爆发。

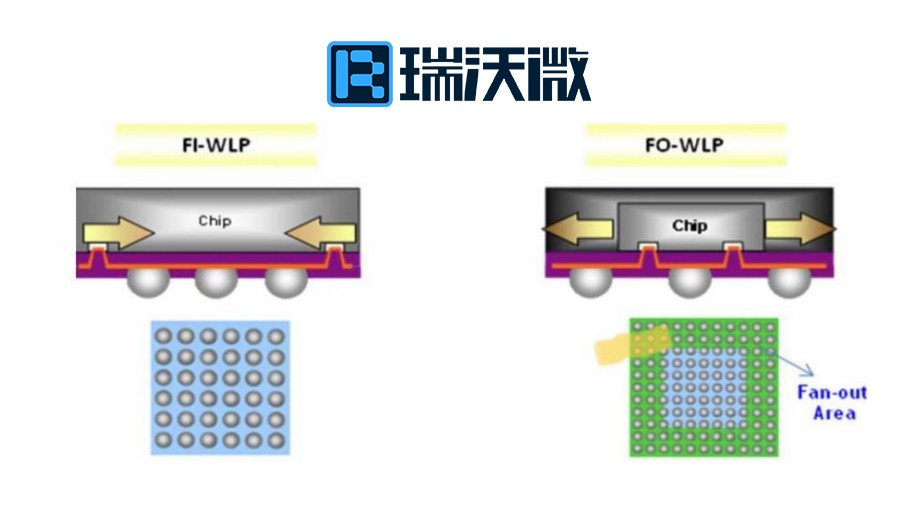

今天我们来了解一下晶圆级芯片封装技术扇出型,随着封装技术的发展,逐渐出现了扇出式WLCSP。扇出WLCSP初始用于将独立的裸片重新组装或重新配置到晶圆工艺中,并以此为基础,通过批量处理、构建和金属化结构,如传统的扇入式WLCSP后端处理,以形成最终封装。

由于Fan-Out的Bump可以长到Die外面,封装后IC也较die的面积大(1.2倍最大)。

扇出式WLCSP可根据工艺过程分为芯片先上(Die First)和芯片后上(Die Last)。芯片先上工艺,简单地说就是把芯片放上,再做布线(RDL);芯片后上就是先做布线,测试合格的单元再把芯片放上去,芯片后上工艺的优点是可以提高合格芯片的利用率已提高良品率。

随着电子产品不断升级换代,智能手机、5G、AI等新兴市场对封装技术提出了更高要求,使得封装技术朝着高维度、超细节距互连等方向发展。晶圆级封装技术可以减小芯片尺寸、布线长度、焊球间距等,因此可以提高集成电路的集成度、处理器的速度等,降低功耗,提高可靠性,顺应了电子产品日益轻薄短小、低成本的发展需求。

晶圆级封装技术要不断降低成本,提高可靠性水平,扩大在大型IC方面的应用:

● 通过减少WLCSP的层数降低工艺成本,缩短工艺时间,主要是针对I/O少、芯片尺寸小的产品。

● 通过新材料应用提高WLCSP的性能和可靠度。主要针对I/O多、芯片尺寸大的产品。

该文章部分内容来源自互联网,如有侵权请联系删除。