服务热线

18574304394

2024-11-06 09:09:53

由深圳瑞沃微半导体科技有限公司发布 | 2024-11-06 深圳

在半导体技术的快速发展中,封装技术作为连接芯片与外部世界的桥梁,其重要性不言而喻。CSP(Chip Scale Package),即芯片级封装技术,正是近年来备受瞩目的一种先进封装技术。今天,请跟随瑞沃微的脚步,一起深入了解CSP芯片级封装工艺的奥秘。

CSP,顾名思义,其核心理念在于封装尺寸与芯片尺寸的高度接近。相较于传统的封装方式,CSP工艺能够显著减小封装后的体积,同时降低重量,这对于追求小型化、轻量化的现代电子产品而言,无疑是一个巨大的福音。

瑞沃微CSP新型封装工艺已替代传统封装:

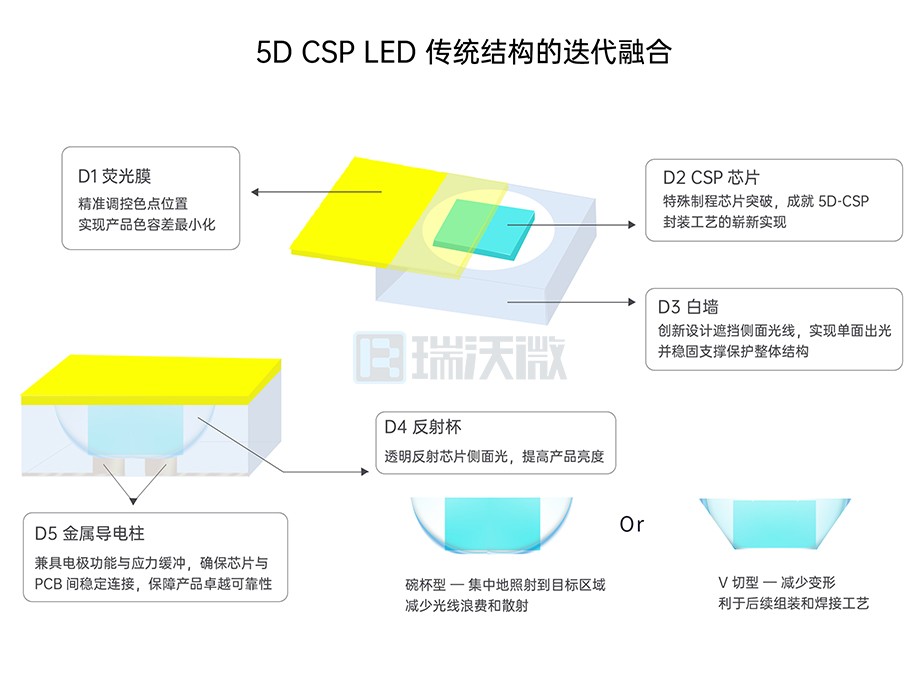

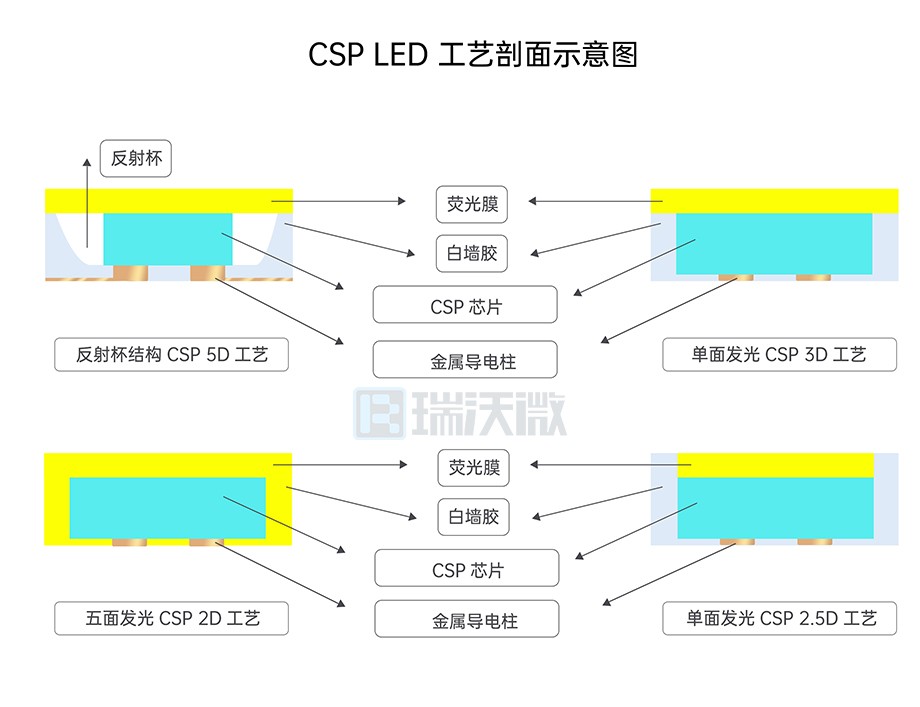

1、CSP 5D封装代表着芯片封装技术的一个全新高度,它预示着在多维空间中实现更高层次的芯片集成。传统的CSP封装主要局限于二维平面的芯片布局,而瑞沃微5D工艺能突破这一限制,探索在三维甚至更多维度上的芯片堆叠与互连。模块化设计和可重构互连技术使得5D封装能够根据不同应用需求进行定制和优化,从而适应未来技术的发展趋势,如异构集成和系统级封装。

2、CSP 3D封装能显著减小封装体积,提高集成度,同时降低功耗和成本,在高性能计算、移动通信等领域中具有广泛应用前景;

3、CSP 2D封装在体积小、重量轻、散热效率高等方面大幅度提升的同时也不会降低良率,因此广泛应用于各类电子产品中;

4、CSP 2.5D封装则是一种介于两者之间的过渡形式,既具有较小的封装体积,又保持了较好的可靠性和稳定性;

值得一提的是,CSP在未来物联网、5G通信等技术的快速发展中,对电子产品封装技术的要求也将越来越高。瑞沃微CSP工艺凭借其小型化、轻量化、高可靠性、低成本等优势,未来有望在更多领域得到应用和推广,为集成电路封装的发展注入新的活力和动力。