服务热线

18574304394

2024-01-09 15:02:00

由深圳瑞沃微半导体科技有限公司发布 | 2024-01-09 深圳

CSP的全名是芯片级封装(Chip Scale Package),就是目前封装业界最怕的无封装制程,如图1 所示,

CSP无需支架、金线等传统封装工艺中必须的主要部件材料及固晶、焊金线等封装主要装备。

CSP的技术定义为将封装体积和LED芯片一致、或是封装体积应不大于LED芯片20%,

且LED仍能具备完整功能的封装器件,而CSP技术所追求的是在器件体积尽可能微缩、减小,

却仍须维持相同芯片所应有的光效,而关键器件体积减小后最直接的特点就能实践低成本、小发光面积、

更长组件使用寿命的设计目的,再加上小体积器件也表示二次光学的相关光学处理优化弹性更高、处理成本更低,

制成的灯具产品能在极小光学结构实践最高亮度与最大发光角度。

CSP封装:CSP: Chip Scale Package

定义:球距(Ball pitch)小于1.0um(通常为0.8mm,0.75m,0.5mm)者称之为芯片维度封装(CSP),

而球距离大于或等于1.0um的称为球格阵列封装(BGA),所以我们通过定义就可以多认识一种叫做BGA的封装形式。

CSP通常分为四种

1.硬式基板型(Rigid substrate)--像小型的BGA

2.软式基板型(Flex substrate)

3.导线架型(Lead frame)

4.晶圆级(Wafer level)

CSP:直接在晶圆上进行大多数或者全部的封装测试程序

1.原晶片尺寸最小的封装方式

2.传输路径短(锡球取代金线)

3.散热特性佳(少了传统密封的塑料包装)

4.主要应用于手机,数码相机(便携式产品

对于CSP封装,我们介绍一种叫做重分布层(RDL)的工艺流程,然后其它类似的方式都可以触类旁通。

CSP封装:CSP: Chip Scale Package

定义:球距(Ball pitch)小于1.0um(通常为0.8mm,0.75m,0.5mm)者称之为芯片维度封装(CSP),

而球距离大于或等于1.0um的称为球格阵列封装(BGA),所以我们通过定义就可以多认识一种叫做BGA的封装形式。

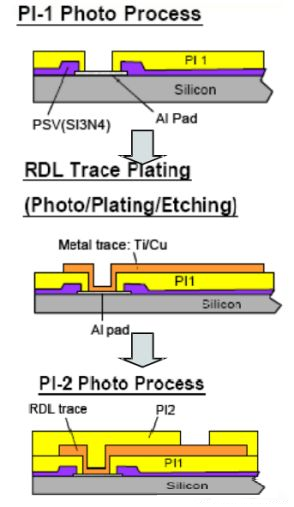

1、先在晶圆上涂布高分子介电材料,目的在增加钝化层的强度(第一层PI),这一层用的高分子介电材料就是Polymide,

它是一种类似光刻胶的材料,也可以通过光刻、显影的方式将需要打开的区域打开,打开的区域就是原来PAD窗口位置,

目的是要淀积一层导电层;

2、所以,第二步就是金属的淀积,比如Ti/cu的淀积,这一层同样需要通过光刻,

刻蚀的方法将不要的区域刻蚀掉,这样做的目的除了是要保证去除不要的区域外,

另外的目的就是把原来PAD窗口的位置通过金属转移到另一个位置,这个位置面积足够大,

能够容纳锡铅球的大小,因为锡铅球一般比较大,而PAD原本设置的位置一般距离比较小,为了保证封装面积足够小,

通过将需要连接的位置转移、分散,从而实现电气连接;

3、第三步还是同样的淀积Polymide,然后同样的将需要安置锡铅球的位置的区域打开;

4、然后淀积另一层金属:Ti/Cu,在通过光刻、刻蚀的方法开出连接锡铅球的区域;

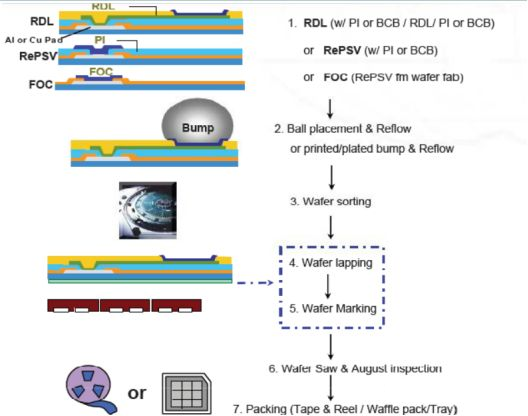

5、最后一步是锡铅球的形成步骤,先上助焊剂,再上锡铅球,再进行Re-flow,完成锡铅球。

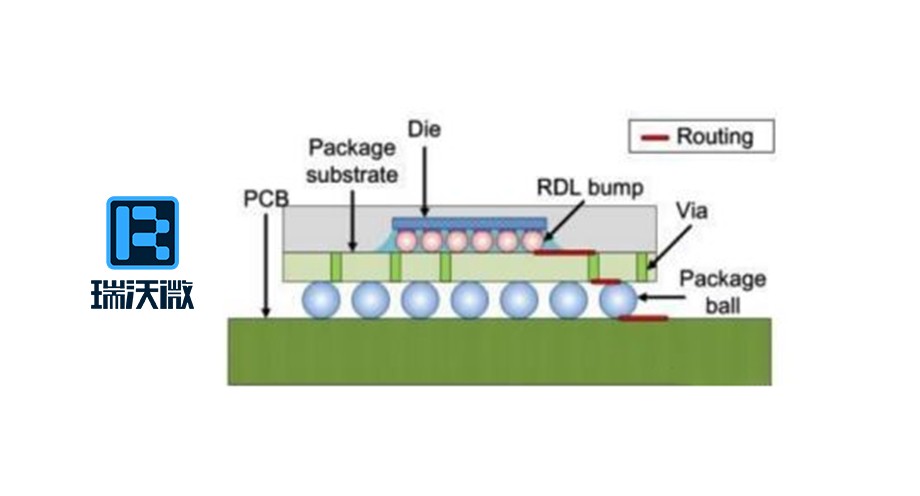

要完成与PCB版的连接,还需要通过Via和金属与Package ball完成电气连接,见如下示意图。

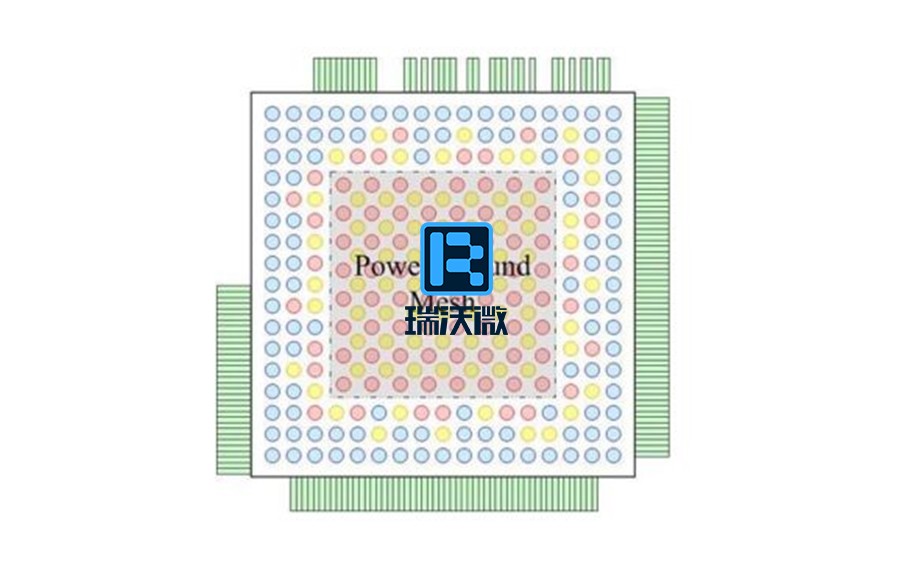

CSP封装的俯视图见下面,锡铅球很多,很复杂,其对不同IO接口如何分配锡铅球有着一定的规则,这里就不介绍了,

大家能够了解CSP封装是如何操作的就可以了。

来看一下整体:RDL,RePSV,FOC形式类似,是根据实际锡铅球大小、分布来选择的。

最后,CPS封装一般会采用晶圆级封装形式,前面讲的步骤都在晶圆厂中进行。

注明:本文转载至半导体内功修炼,如有侵权请联系删除